Chiedi a un esperto

La definizione della soluzione più adeguata richiede un'approfondita conoscenza delle caratteristiche necessarie ai sistema e al progetto. Lasciatevi guidare dagli esperti Kingston.

Chiedi a un esperto

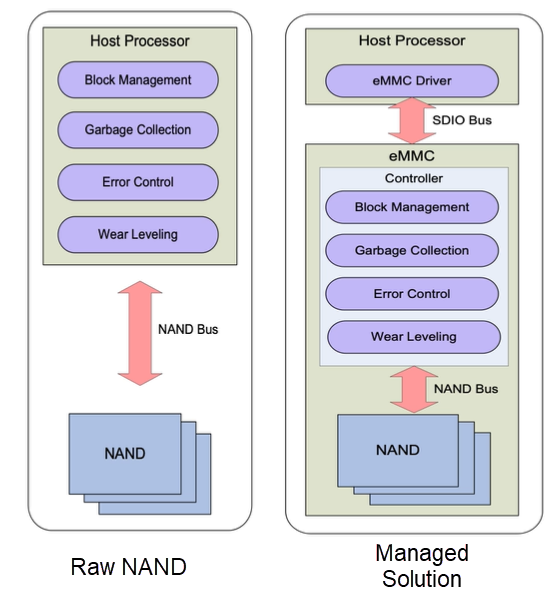

Lo storage Flash NAND non è un semplice strumento di gestione dati in lettura/scrittura. Per garantire un funzionamento affidabile, è necessario implementare numerosi algoritmi: Gestione dei blocchi NAND, garbage collection, controllo degli errori e livellamento dell’usura. Le moderne memorie NAND Flash sono di tipo gestito, con algoritmi installati sul dispositivo di storage e non implementati sul processore host. Questo approccio garantisce maggiori vantaggi per gli utenti, in quanto riduce la complessità dei processi di gestione NAND per l'host e semplifica i processi di supporto e manutenzione del prodotto.

I processi di scrittura dell'host sulla NAND flash sono caratterizzati da inefficienze che possono causare guasti prematuri del dispositivo. La più piccola unità organizzativa delle NAND è costituita dalla pagina, che può essere letta e programmata ma non cancellata. La sola unità organizzativa che può essere cancellata è il blocco, che è composto da numerose pagine. Pertanto, le pagine non possono essere sovrascritte fino a quando il blocco non viene cancellato. Col passare del tempo, i blocchi possono diventare corrotti con il graduale approssimarsi dell'esaurimento del loro ciclo di vita. In tali casi si possono anche verificare difetti che producono guasti prematuri.

Le memorie NAND flash offrono un numero limitato di cicli di programmazione cancellazione. Una volta raggiunto tale limite, il dispositivo entra nel periodo di fine di ciclo di vita EOL, durante il quale è da considerarsi non più affidabile. La durata dei dispositivi varia in base alla configurazione delle celle NAND.

Configurazione a celle singole: Questa configurazione garantisce la massima durata e il più elevato margine di errore.

|

eMMC LBA 512B Sector Address |

NAND Page & Block Address |

| 0:31 | Blk10, Pg101 |

| 32:63 | Blk10, Pg102 |

| 64:95 | Blk10, Pg103 |

| 96:127 | Blk10, Pg104 |

| 128:159 | Blk15, Pg57 |

| 160:191 | Blk8, Pg129 |

| 192:223 | Blk10, Pg107 |

| 224:255 | Blk22, Pg88 |

La memoria eMMC consente la lettura e scrittura di unità di settore a 512 byte virgola che sono di tipo logico e non fisico. Gli indirizzi di settore sono denominati indirizzi di blocco logici, o LBA. Quando i dati vengono modificati, non è pratico eliminare l'intero blocco NAND, causando usure inefficienti sulle pagine che non sono state modificate. Pertanto uno schema di mappatura LBA-PBA (Physical Block Address) consente alle sezioni che ospitano scritture ridotte di effettuare il bilanciamento dell'usura dei blocchi, mediante una pratica nota come livellamento dell'usura. Attraverso l'uso di una tabella di traduzione degli indirizzi, gli LBA vengono mappati sui PBA. Questo processo effettua il bilanciamento dell'usura sui blocchi e migliora anche la velocità di scrittura.

Il processo di mappatura degli indirizzi funziona nel modo seguente:

Normalmente, le riscritture di piccole dimensioni casuali su pagine non allineate rappresentano la principale sorgente di amplificazione in scrittura. Al fine di minimizzare il valore WAF, le scritture devono essere allineate sui margini di una pagina utilizzando unità multiple della dimensione di pagina. Questa dimensione di unità ottimale, rappresenta il campo di dimensione in scrittura ottimale per il registro Extended CSD.

La formula per determinare i byte totali scritti, o TBW, è piuttosto semplice:

Spesso il parametro WAF è compreso tra 4 e 8, ma tale valore dipende dal comportamento in scrittura del sistema di hosting. Per esempio, scritture sequenziali di grandi dimensioni generano un WAF inferiore, mentre scritture casuali di blocchi dati di piccole dimensioni producono un WAF superiore. Questo tipo di comportamento può spesso portare a prematuri danneggiamenti dai dispositivi di storage.

Per esempio, un dispositivo EMMC da 4 GB con fattore di durata pari a 3000 e fattore WAF pari a 8 equivale a:

Il numero di bit totali scritti sul dispositivo eMMC è pari a 1,5 TB. Pertanto, è possibile scrivere 1,5 TB di dati durante l'intero ciclo di vita del prodotto prima che questo entri in modalità EOL.

Per determinare i vostri requisiti TBW, e necessario fare una stima dell'utilizzo giornaliero del dispositivo in questione. Per esempio, un carico di lavoro pari a 500 MB di scritture giornaliera con un ciclo di vita prestabilito pari a 5 anni, richiederà un dispositivo in grado di garantire un valore TBW superiore a 915 GB:

Il parametro TBW Può essere utilizzato per determinare il valore WAF massimo consentito in quanto il valore TBW = (DC * EF) / WAF. Se la durata del dispositivo non è in grado di raggiungere il valore TBW target per l'applicazione di prodotto, è possibile cercare di migliorarlo. Prendere in considerazione l'ipotesi di impostare il dispositivo in modalità Pseudo Single Level Cell che può consentire un incremento della durata 10 volte superiore convertendo il dispositivo da TLC a MLC in modalità a bit singolo per cella. Tuttavia l'uso di questa modalità causa una drastica riduzione della capacità: Il 50% per un dispositivo MLC a due bit per cella, e oltre il 66% per un dispositivo TLC a tre bit per cella. Qualora tale soluzione non dovesse essere soddisfacente per le vostre esigenze, potrebbe essere utile scegliere un dispositivo di dimensioni maggiori per gestire il medesimo tipo di carico di lavoro. Un dispositivo che offre una capacità doppia garantisce anche un valore TBW raddoppiato.

Gli algoritmi eMMC di Kingston garantiscono un fattore di amplificazione in scrittura estremamente ridotto. Offriamo molteplici configurazioni che garantiscono un perfetto equilibrio tra prestazioni, durata e affidabilità. L'età del dispositivo può essere monitorata utilizzando gli strumenti di valutazione della durata JEDEC contenuti in EXT_CSD, una funzionalità integrata in tutti i dispositivi eMMC. La durata viene indicata mediante incrementi del 10% in base alla durata totale del dispositivo. Uno strumento indica l'età dei blocchi NAND flash con configurazione TLC o MLC, mentre l'altro indica l'età dei blocchi configurati in modalità pseudo SLC. I dispositivi Kingston eMMC integrano anche comandi proprietari che consentono il ripristino dell'età del dispositivo al valore medio. Questi strumenti sono più oculati rispetto a quelli JEDEC ma richiedono sviluppo software per poter essere utilizzati. In alternativa, è possibile inviare il dispositivo obsoleto presso Kingston per un'analisi più completa.

#KingstonIsWithYou

La definizione della soluzione più adeguata richiede un'approfondita conoscenza delle caratteristiche necessarie ai sistema e al progetto. Lasciatevi guidare dagli esperti Kingston.

Chiedi a un esperto

La longevità del prodotto è una preoccupazione fondamentale per molte applicazioni embedded che in genere richiedono una durata di 7-10 anni. Dato il ritmo veloce con cui la tecnologia avanza e cambia, il sostegno a lungo termine dei prodotti integrati può essere difficile.

È importante capire come vengono gestite le memorie NAND Flash su dispositivi eMMC e come tale relazione influenza il ciclo di vita. Questa guida aiuta progettisti e ingegneri a capire come valutare e convalidare il ciclo di vita utile di un dispositivo di storage eMMC nell’ambito del design dei loro sistemi.