ได้รับการรับรองโดยผู้ผลิตเมนบอร์ดชั้นนำของโลก{{Footnote.N64682}}

ผ่านการทดสอบและรับรองแล้ว คุณจึงสามารถเลือกประกอบและอัพเกรดได้อย่างมั่นใจกับเมนบอร์ดที่คุณเลือกเอง

DDR5 คือ Double Data Rate Synchronous Dynamic Random Access Memory รุ่นที่ 5 เรียกอีกชื่อว่า DDR5 SDRAM เริ่มต้นจากเมื่อปี 2017 โดย JEDEC (Joint Electron Device Engineering Council) หน่วยงานกำหนดมาตรฐานอุตสาหกรรมโดยการประสานข้อมูลจากผู้ผลิตเซมิคอนดัคเตอร์และชิปเซ็ตหน่วยความจำชั้นนำของโลก รวมทั้ง Kingston หน่วยความจำ DDR5 ออกแบบมาพร้อมคุณสมบัติการทำงานใหม่ ๆ ที่มีประสิทธิภาพเหนือกว่า ใช้กระแสไฟน้อยกว่าและจัดการข้อมูลได้อย่างเชื่อถือได้มากกว่าเพื่อเตรียมพร้อมสำหรับการประมวลผลแห่งทศวรรษใหม่ DDR5 เปิดตัวในปี 2021

DDR5 มีความเร็วเริ่มต้นที่ 4800MT/s{{Footnote.A65242}} ในขณะที่ DDR4 มีความเร็วไม่เกิน 3200MT/s นั่นเท่ากับว่ามีแบนด์วิธเพิ่มขึ้นถึง 50% ยิ่งไปกว่านั้น DDR5 ยังมีแผนจะกำหนดความเร็วมาตรฐานที่อาจสูงถึง 8800MT/s หรือมากกว่านั้นเพื่อให้สอดคล้องกับการอัปเดตแพลตฟอร์มคอมพิวเตอร์

DDR5 ใช้กระแสไฟเพียง 1.1V ซึ่งน้อยกว่า DDR4 ซึ่งใช้ไฟที่ 1.2V ถึง 20% นอกจากช่วยยืดเวลาการใช้งานแบตเตอรี่ให้กับโน้ตบุ๊กแล้ว หน่วยความจำนี้ยังมีข้อดีสำคัญสำหรับเซิร์ฟเวอร์ระดับองค์กรที่ต้องทำงานอยู่ตลอดเวลาเช่นกัน

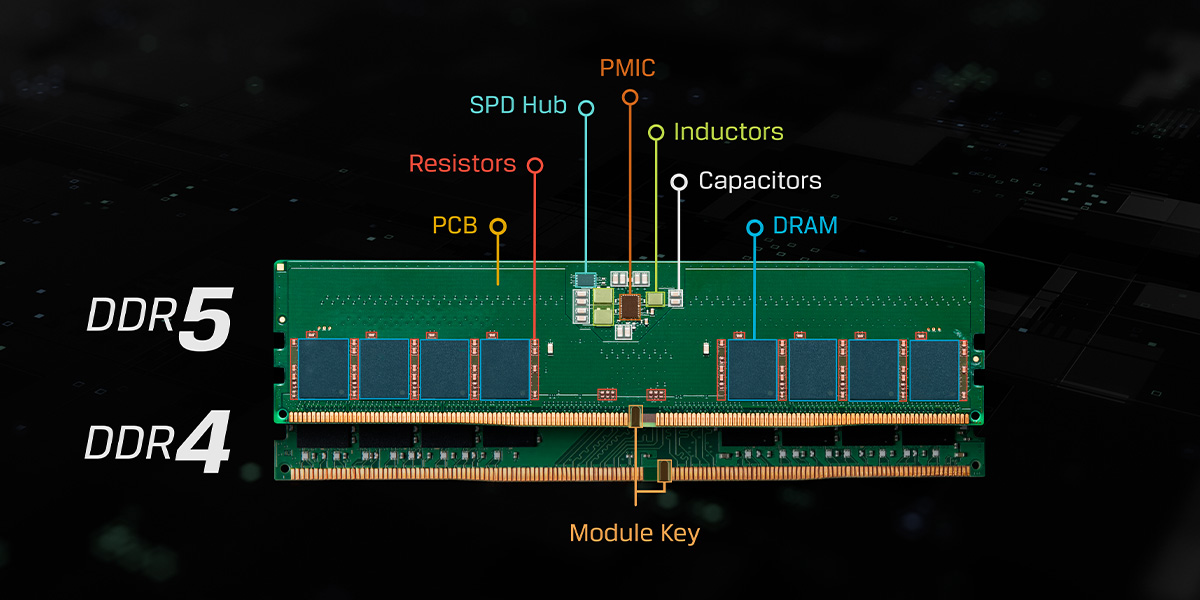

หน่วยความจำ DDR5 มาพร้อมกับ Power Management Integrate Circuits (PMIC) ในตัวที่ทำหน้าที่ควบคุมกระแสไฟฟ้าที่ส่วนประกอบต่าง ๆ ของโมดูลหน่วยความจำใช้ (DRAM, รีจิสเตอร์, ฮับ SPD ฯลฯ) สำหรับโมดูลระดับเซิร์ฟเวอร์ PMIC ใช้กระแสไฟที่ 12V ส่วนรุ่นสำหรับ PC ตัว PMIC จะใช้กระแสไฟที่ 5V ซึ่งทำให้การจัดสรรพลังงานดีกว่ารุ่นก่อนหน้า ความสมบูรณ์ของสัญญาณดีขึ้น และลดสัญญาณรบกวนลง

DDR5 เลือกใช้อุปกรณ์ใหม่ที่ทำงานร่วมกับ Serial Presence Detect (SPD) EEPROM พร้อมคุณสมบัติในการทำงานของฮับเพิ่มเติม เพื่อจัดการการใช้งานกับชุดควบคุมจากภายนอก และเพื่อลดภาระของหน่วยความจำที่บัสภายในออกจากส่วนการทำงานภายนอก

DDR5 จะแยกโมดูลหน่วยความจำออกเป็นช่องสัญญาณย่อยที่ระบุที่อยู่ได้ขนาด 32 บิตสองช่องสัญญาณที่เป็นอิสระจากกันเพื่อเพิ่มประสิทธิภาพ และลดค่าหน่วงเวลาในการสืบค้นข้อมูลสำหรับชุดควบคุมหน่วยความจำ ขอบเขตความกว้างของข้อมูลของโมดูล DDR5 ยังคงทำงานแบบ 64 บิต แต่การแยกย่อยออกเป็นช่องสัญญาณแบบระบุที่อยู่ได้สองช่องขนาด 32 บิตทำให้ประสิทธิภาพในการทำงานโดยรวมดีขึ้น สำหรับหน่วยความจำระดับเซิร์ฟเวอร์ (RDIMM) การทำงานขนาด 8 บิตได้ถูกเสริมเข้ามาสำหรับช่องสัญญาณย่อยแต่ละส่วนเพื่อรองรับการทำงานกับ ECC ทำให้รองรับการทำงานต่อช่องสัญญาณย่อยรวมได้มากถึง 40 บิต หรือ 80 บิตต่อแถวโมดูลหน่วยความจำ โมดูลแบบสองแถวมีจุดเด่นที่การจัดสรรช่องสัญญาณการสื่อสารย่อยแบบ 32 บิตสี่ช่องสัญญาณ

ร่องบากตรงกลางของโมดูลทำหน้าที่เป็นคีย์กำกับแนวสำหรับซ็อคเก็ต DDR5 เพื่อป้องกันการติดตั้งกับ DDR4, DDR3 หรือโมดูลอื่น ๆ ที่ไม่รองรับ คีย์โมดูล DDR5 จะแตกต่างจาก DDR4 ตามประเภทของโมดูลได้แก่ UDIMM และ RDIMM

On-Die ECC (Error Correction Code) เป็นคุณสมบัติใหม่ที่ออกแบบมาเพื่อแก้ไขข้อผิดพลาดของบิตข้อมูลภายในชิป DRAM เนื่องจากชิป DRAM มีความหนาแน่นเพิ่มมากขึ้นโดยการย่อขนาดของชั้นเวเฟอร์ลง ทำให้การรั่วไหลของข้อมูลเพิ่มมากขึ้น On-Die ECC ช่วยลดความเสี่ยงนี้โดยการแก้ไขข้อผิดพลาดภายในชิป ทำให้การทำงานมีเสถียรภาพมากขึ้นและอัตราข้อผิดพลาดน้อยลง เทคโนโลยีนี้ไม่สามารถแก้ไขข้อผิดพลาดภายนอกชิปได้ หรือข้อผิดพลาดที่เกิดขึ้นกับบัสระหว่างโมดูลและชุดควบคุมหน่วยความจำภายใน CPU โปรเซสเซอร์ที่ใช้ ECC สำหรับเซิร์ฟเวอร์และเวิร์คสเตชั่นจะมีการเข้ารหัสที่สามารถแก้ไขข้อผิดพลาดแบบบิตเดียวหรือหลายบิตได้ระหว่างการทำงาน DRAM จะต้องมีบิตเพิ่มเติมเพื่อให้สามารถแก้ไขข้อผิดพลาดนี้ได้ ซึ่งเป็นสิ่งที่คาดหวังได้จากโมดูลคลาส ECC เช่น ECC unbuffered, Registered และ Load Reduced

DDR5 RDIMM ระดับเซิร์ฟเวอร์จะมีเซ็นเซอร์วัดอุณหภูมิเพิ่มเข้ามาที่ท้ายโมดูลเพื่อตรวจสอบอุณหภูมิตลอดแนวของ DIMM ทั้งนี้เพื่อให้สามารถควบคุมการทำความเย็นให้กับระบบได้แม่นยำมากขึ้นและเป็นการแก้ปัญหาที่พบใน DDR4 เนื่องจากอุณหภูมิที่สูงเกิน

DDR5 รองรับแถวโมดูลติดตั้งเพิ่มขึ้นเป็นสองเท่าจาก 16 เป็น 32 แถว ทำให้เปิดเพจต่อครั้งได้มากกว่าเดิม ประสิทธิภาพในการทำงานจึงมากกว่าเดิม นอกจากนี้ความยาวเบิร์สขั้นต่ำยังถูกปรับเพิ่มจาก 16 จากเดิมที่ 8 สำหรับ DDR4 วิธีการนี้ช่วยเสริมประสิทธิภาพในการทำงานของบัสข้อมูล ทำให้บัสรองรับข้อมูลมากเป็นสองเท่าและยังช่วยลดจำนวนการอ่าน/เขียนข้อมูลไปยังช่องข้อมูลแคชเดียวกัน

DDR5 มาพร้อมกับชุดคำสั่งใหม่คือ SAME-BANK Refresh ซึ่งทำให้สามารถรีเฟรชข้อมูลในกลุ่มแถวหน่วยความจำได้แบบแถวต่อแถวแทนที่จะต้องรีเฟรชทุกแถว เมื่อเปรียบเทียบกับ DDR4 คำสั่งนี้ช่วยให้ DDR5 สามารถปรับปรุงประสิทธิภาพในการทำงานและการประหยัดพลังงานให้เหนือกว่าเดิม

เพื่อให้สัญญาณการสื่อสารของโมดูลมีเสถียรภาพ ซึ่งจำเป็นสำหรับการทำงานที่ใช้แบนด์วิธสูง

แม้ว่าโมดูลหน่วยความจำเองจะมีลักษณะใกล้เคียงกับ DDR4 แต่ก็มีการเปลี่ยนแปลงที่สำคัญ ๆ ที่ทำให้ไม่สามารถใช้กับระบบการทำงานแบบเก่าได้ ตำแหน่งของคีย์ (ร่องบากตรงกลาง) ถูกปรับเปลี่ยนเพื่อป้องกันไม่ให้มีการติดตั้งกับซ็อคเก็ตที่ไม่รองรับ

ผ่านการทดสอบและรับรองแล้ว คุณจึงสามารถเลือกประกอบและอัพเกรดได้อย่างมั่นใจกับเมนบอร์ดที่คุณเลือกเอง

| อัตราการสืบค้นข้อมูล (ความเร็วเป็น MT/s){{Footnote.A65242}} | 3600, 4000, 4400, 4800, 5200, 5600, 6000, 6400, 6800, 7200, 7600, 8000, 8400, 8800 |

| ความหนาแน่นของ Monolithic DRAM (Gbit) | 8Gb, 16Gb, 24Gb, 32Gb, 48Gb, 64Gb |

| ประเภทชุดบรรจุและโครงร่าง (x4, x8 / x16) | BGA, 3DS TSV (78, 82 / 102) |

| อินเทอร์เฟซ | |

|---|---|

| แรงดันไฟฟ้า (VDD / VDDQ / VPP) | 1.1 / 1.1 / 1.8 V |

| Internal VREF | VREFDQ, VREFCA, VREFCS |

| คำสั่ง/ที่อยู่อ้างอิง | POD (Pseudo Open Drain) |

| อีควอไลเซชั่น | DFE (Dynamic Feedback Equalization) |

| ความยาวเบิร์ส | BL16 / BC8 / BL32 (ฟังก์ชั่นเสริม) |

| สถาปัตยกรรมหลัก | |

| จำนวนแถว | 32 แถว (8 กลุ่มแถวติดตั้ง) 8 BG x 4 แถว (16-64Gb x4/x8) 8 BG x 2 แถว (8Gb x4/x8) 16 แถว (4 กลุ่มแถวติดตั้ง) 4 BG x 4 แถว (16-64Gb x16) 4 BG x 2 แถว (8Gb x16) |

| ขนาดเพจ (x4 / x8 / x16) | 1KB / 1KB / 2KB |

| Prefetch | 16n |

| DCA (Duty Cycle Adjustment) | DQS และ DQ |

| ระบบตรวจสอบความหน่วง DQS ภายใน | DQS interval oscillator |

| ODECC (On-die ECC) | 128b+8b SEC error check and scrub |

| CRC (Cyclic Redundancy Check) | อ่าน/เขียน |

| ODT (On-die Termination) | DQ, DQS, DM, บัส CA |

| MIR (ขาต่อ “จำลอง”) | ใช่ |

| Bus Inversion | Command/address inversion (CAI) |

| CA Training, CS Training | CA training, CS training |

| โหมดแนะนำการเกลี่ยการเขียนข้อมูล | ปรับปรุงให้ดีขึ้น |

| รูปแบบการแนะนำการอ่านข้อมูล | MR แยกเฉพาะเพื่อรองรับรูปแบบการกำกับการทำงานแบบอนุกรม ผ่านสัญญาณนาฬิกาและ LFSR ที่ผู้ใช้กำหนด |

| รีจิสเตอร์บันทึกโหมดการทำงาน | สูงสุด 256 x 8 บิต |

| คำสั่ง PRECHARGE | ทุกแถว ต่อแถวหรือแถวเดียวกัน |

| คำสั่ง REFRESH | ทุกแถวและแถวเดียวกัน |

| โหมด Loopback | ใช่ |