Kualifikasi produsen motherboard terkemuka di dunia{{Footnote.N64682}}

Telah diuji dan disetujui sehingga Anda dapat menyusun dan meng-upgrade motherboard pilihan Anda dengan percaya diri.

DDR5 adalah generasi ke-5 dari Double Data Rate Synchronous Dynamic Random Access Memory, alias DDR5 SDRAM. Dimulai pada tahun 2017 oleh badan standar industri JEDEC (Dewan Rekayasa Perangkat Elektron Gabungan/Joint Electron Device Engineering Council) dengan masukan dari para vendor semikonduktor memori dan arsitektur chipset global terkemuka, termasuk Kingston, DDR5 dirancang dengan fitur-fitur baru untuk kinerja lebih tinggi, penggunaan daya lebih rendah, dan integritas data lebih kuat untuk komputasi pada dekade berikutnya. DDR5 diluncurkan pada tahun 2021.

DDR5 diawali dengan kecepatan 4800MT/dtk{{Footnote.A65242}}, sedangkan DDR4 mencapai kecepatan maksimum pada 3200MT/dtk. Perbedaan ini menunjukkan peningkatan bandwidth sebesar 50%. Sesuai dengan rilis platform komputasinya, rencana kecepatan standar DDR5 akan ditingkatkan hingga 8800MT/dtk, bahkan dapat lebih dari itu.

Pada 1,1 V, DDR5 mengonsumsi daya ~20% lebih sedikit daripada komponen setara DDR4 pada 1,2 V. Selain memperpanjang usia baterai di laptop, DDR5 juga memiliki keunggulan signifikan untuk server perusahaan besar yang bekerja sepanjang waktu.

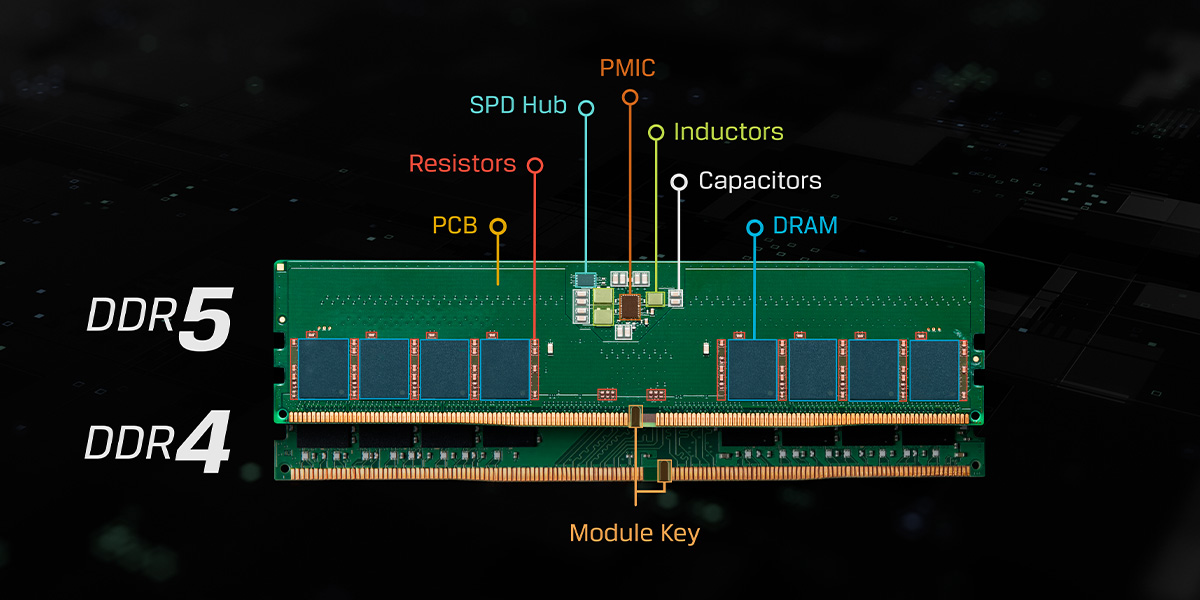

Modul DDR5 memiliki fitur Power Management Integrate Circuits (PMIC) on-board, yang membantu mengatur daya yang dibutuhkan oleh berbagai komponen modul memori (DRAM, Register, hub SPD, dll). Untuk modul kelas server, PMIC menggunakan 12 V dan untuk modul kelas PC, PMIC menggunakan 5 V. Hal ini membuat distribusi daya lebih baik daripada generasi sebelumnya, meningkatkan integritas sinyal, dan mengurangi derau.

DDR5 menggunakan perangkat baru yang mengintegrasikan EEPROM Serial Presence Detect (SPD) dengan fitur hub tambahan, yang mengelola akses ke pengontrol eksternal dan memisahkan beban memori pada bus internal dari eksternal.

DDR5 memisahkan modul memori menjadi dua subkanal 32-bit independen yang dapat dialamatkan untuk meningkatkan efisiensi dan menurunkan latensi akses data untuk pengontrol memori. Lebar data dari modul DDR5 masih 64-bit, tetapi dengan membaginya menjadi dua kanal 32-bit yang dapat dialamatkan, meningkatkan kinerja keseluruhan. Untuk memori kelas server (RDIMM), 8-bit ditambahkan ke setiap subkanal untuk dukungan ECC dengan total 40-bit per subkanal, atau 80-bit untuk setiap Rank. Modul Dual Rank mempunyai fitur empat subkanal 32-bit.

Alur di tengah modul berfungsi seperti kunci, yang diselaraskan dengan soket DDR5 untuk mencegah dipasangnya DDR4, DDR3, atau jenis modul lain yang tidak didukung. Tidak seperti DDR4, kunci modul DDR5 berbeda antara jenis modul: UDIMM dan RDIMM

On-Die ECC (Error Correction Code), atau Kode Koreksi Kesalahan pada Cetakan, adalah fitur baru yang dirancang untuk mengoreksi kesalahan bit di dalam chip DRAM. Saat chip DRAM meningkat kepadatannya melalui penyusutan litografi wafer, potensi kebocoran data meningkat. On-Die ECC mengurangi risiko ini dengan mengoreksi kesalahan dalam chip, yang meningkatkan keandalan dan mengurangi tingkat kerusakan. Teknologi ini tidak dapat mengoreksi kesalahan di luar chip atau yang terjadi pada bus antara modul dan pengontrol memori yang terdapat di dalam CPU. Prosesor dengan pengaktifan ECC untuk server dan stasiun kerja mempunyai fitur pengkodean yang dapat mengoreksi kesalahan bit-tunggal atau multi-bit pada saat proses berjalan. Bit DRAM tambahan harus tersedia untuk memungkinkan koreksi ini terjadi, yang merupakan fitur pada tipe modul kelas ECC seperti ECC unbuffered (tanpa buffer), Registered (terdaftar), dan Load Reduced (pengurangan beban).

RDIMM DDR5 kelas server menambahkan sensor suhu pada ujung modul untuk memantau kondisi termal di sepanjang modul DIMM. Dengan penambahan ini, kontrol pendinginan sistem menjadi lebih tepat, sehingga tidak terjadi hambatan kinerja seperti yang dialami oleh DDR4 pada suhu tinggi.

DDR5 menggandakan bank dari 16 menjadi 32. Ini memungkinkan lebih banyak page dibuka pada satu saat, yang meningkatkan efisiensi. Selain itu, panjang burst minimum juga digandakan menjadi 16, naik dari 8 untuk DDR4. Hal ini meningkatkan efisiensi bus data, menyediakan dua kali data pada bus, dan akibatnya mengurangi jumlah baca/tulis untuk mengakses jalur data cache yang sama.

DDR5 menambahkan perintah baru yang disebut SAME-BANK Refresh, yang memungkinkan refresh hanya satu bank per grup bank, versus semua bank. Jika dibandingkan dengan DDR4, perintah ini memungkinkan DDR5 untuk lebih meningkatkan kinerja dan efisiensi.

DDR5 menggunakan Decision Feedback Equalization (DFE) untuk memberikan integritas sinyal yang stabil dan andal pada modul, yang diperlukan untuk bandwidth tinggi.

Meskipun modul memorinya sendiri tampak serupa dengan DDR4, terdapat perubahan signifikan yang membuatnya tidak kompatibel dengan sistem lama. Lokasi alur pemandu (takik di bagian tengah) dibuat berbeda untuk mencegah pemasangan modul ke soket yang tidak kompatibel.

Telah diuji dan disetujui sehingga Anda dapat menyusun dan meng-upgrade motherboard pilihan Anda dengan percaya diri.

| Kecepatan Data (Kecepatan dalam MT/s){{Footnote.A65242}} | 3600, 4000, 4400, 4800, 5200, 5600, 6000, 6400, 6800, 7200, 7600, 8000, 8400, 8800 |

| Kepadatan DRAM Monolitik (Gbit) | 8Gb, 16Gb, 24Gb, 32Gb, 48Gb, 64Gb |

| Jenis Paket dan Ballout (x4, x8 / x16) | BGA, 3DS TSV (78, 82 / 102) |

| Antarmuka | |

|---|---|

| Voltase (VDD / VDDQ / VPP) | 1,1 / 1,1 / 1,8 V |

| Internal VREF | VREFDQ, VREFCA, VREFCS |

| Perintah/Alamat | POD (Pseudo Open Drain) |

| Penyamaan | DFE (Dynamic Feedback Equalization/Penyamaan Umpan Balik Dinamis) |

| Panjang Burst | BL16 / BC8 / BL32 (opsional) |

| Arsitektur Inti | |

| Jumlah Bank | 32 Bank (8 Grup Bank) 8 BG x 4 bank (16-64 Gb x4/x8) 8 BG x 2 bank (8 Gb x4/x8) 16 Bank (4 Grup Bank) 4 BG x 4 bank (16-64 Gb x16) 4 BG x 2 bank (8 Gb x16) |

| Ukuran Page (x4 / x8 / x16) | 1KB / 1KB / 2KB |

| Prefetch | 16n |

| DCA (Duty Cycle Adjustment/Penyesuaian Siklus Tugas) | DQS dan DQ |

| Internal DQS Delay Monitoring (Pemantauan Keterlambatan DQS Internal) | DQS interval oscillator (Osilator interval DQS) |

| ODECC (On-die ECC/ECC Pada Cetakan) | 128b+8b SEC pemeriksaan dan penghapusan kesalahan |

| CRC (Cyclic Redundancy Check/Pemeriksaan Redundansi Bersiklus) | Baca/Tulis |

| ODT (On-die Termination/Terminasi Pada Cetakan) | DQ, DQS, DM, bus CA |

| MIR (pin “Mirror”) | Ya |

| Inversi Bus | Command/address inversion (CAI) atau inversi perintah/alamat |

| Pelatihan CA, Pelatihan CS | pelatihan CA, pelatihan CS |

| Write Leveling Training Modes (Mode Pelatihan Perataan Tulis) | Ditingkatkan |

| Pola Pelatihan Baca | MR khusus untuk serial, clock, dan LFSR yang ditentukan pengguna -pola pelatihan yang dihasilkan |

| Mode registers | Hingga 256 x 8 bit |

| Perintah PRECHARGE | Semua bank, per bank, dan bank yang sama |

| Perintah REFRESH | Semua bank dan bank yang sama |

| Mode Loopback | Ya |