Reconhecida e testada pelos fabricantes{{Footnote.N64682}} de placas-mãe mais importantes do mundo

Testada e aprovada, assim você pode montar o seu PC ou atualizar com confiança sua placa-mãe preferida.

A DDR5 é a 5a geração da Double Data Rate Synchronous Dynamic Random Access Memory, também conhecida como DDR5 SDRAM. Começando em 2017 pela entidade de padrões industriais JEDEC (Joint Electron Device Engineering Council) com contribuições dos fornecedores líderes globais de arquitetura de chipset e semicondutores de memória, incluindo a Kingston, a DDR5 foi projetada com novos recursos para maior desempenho, menos energia e uma integridade de dados mais sólida para a próxima década da computação. A DDR5 foi lançada em 2021.

A DDR5 começa em 4800Mt/s{{Footnote.A65242}}, enquanto a DDR4 chega até 3200MT/s. Isso representa 50% de aumento da largura de banda. Acompanhando os lançamentos das plataformas de computação, a DDR5 planejou velocidades padrão que chegam a 8800Mt/s, possivelmente além.

A 1.1V, a DDR5 consome aprox. 20% menos energia do que os componentes equivalentes da DDR4 a 1.2V. Enquanto conserva a vida da bateria em laptops, ela também possui uma vantagem significativa para servidores empresariais trabalhando dia e noite.

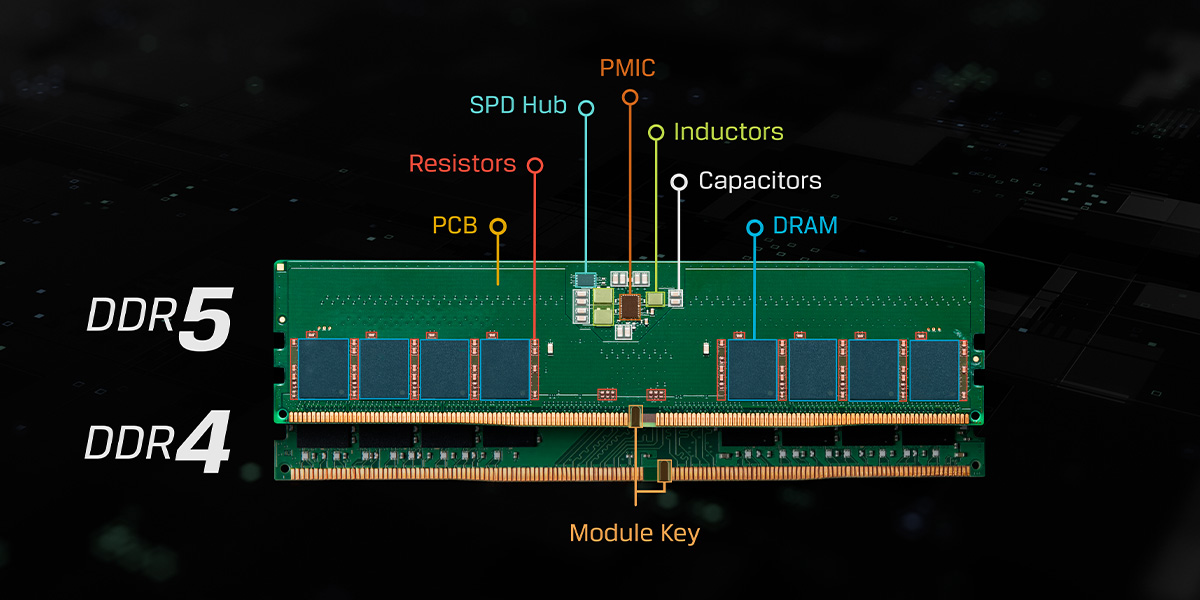

Os módulos DDR5 contam com Circuitos Integrados de Gerenciamento de Energia (PMIC), que ajuda a regular a energia necessária pelos vários componentes do módulo de memória (DRAM, Register, hub SPD etc). Para módulos de servidor o PMIC utiliza 12V, e para módulos de PC o PMIC utiliza 5V. Isso melhora a distribuição de energia melhor do que as gerações anteriores, melhora a integridade do sinal e reduz os ruídos.

A DDR5 utiliza um novo dispositivo integrando a Detecção de Presença em Série (SPD) EEPROM com recursos adicionais de hub, gerenciando o acesso ao controlador externo e desassociando a carga de memória no barramento interno do externo.

A DDR5 divide o módulo de memória em dois acessíveis subcanais de 32-bit independentes para aumentar a eficiência e diminuir as latências de acessos de dados para o controlador de memória. A largura de dados do módulo DDR5 ainda é 64-bit, entretanto dividir em dois canais de 32-bit acessíveis aumenta o desempenho geral. Para memórias de classe de servidor (RDIMMs), 8-bits são adicionados a cada subcanal para suporte de ECC para um total de 40-bits por subcanal, ou 80-bits por Rank. Módulos Dual Rank contam com quatro subcanais de 32-bit.

A fenda no centro do módulo atua como uma chave, alinhando com os soquetes da DDR5 para prevenir que a DDR4, DDR3 ou outros tipos de módulo não compatíveis sejam instalados. Ao contrário da DDR4, as chaves de módulo são diferentes entre os tipos de módulo: UDIMM e RDIMM

On-Die ECC (Código de correção de erro) é um novo recurso projetado para corrigir erros de bit dentro do chip DRAM. Conforme os chips DRAM aumentam em densidade através da diminuição da litografia de placa, o potencial para vazamento de dados aumenta. O On-Die ECC mitiga este risco corrigindo os erros dentro do chip, aumentando a confiabilidade e reduzindo as taxas de defeitos. Esta tecnologia não pode corrigir erros fora do chip ou que ocorram no barramento entre o módulo e o controlador de memória abrigado dentro da CPU. Os processadores habilitados para ECC para servidores e estações de trabalho apresentam o código que pode corrigir erros de bit múltiplo ou único rapidamente. Bits de DRAM extra devem estar disponíveis para essa correção ocorrer, incluídos em tipos de módulo de classe ECC como ECC sem buffer, registrado e de carga reduzida.

RDIMMs DDR5 de classe de servidor adicionam sensores de temperatura às extremidades dos módulos para monitorar condições térmicas no comprimento da DIMM. Isso permite um controle mais preciso para o resfriamento do sistema, em oposição ao desempenho limitado visto na DDR4 para altas temperaturas.

A DDR5 duplica os bancos de 16 para 32. Isso permite que mais páginas sejam abertas de uma vez, aumentando a eficiência. Também duplicou o comprimento do burst mínimo de 16, em relação a 8 da DDR4. Isso aumenta a eficiência do barramento de dados, fornecendo duas vezes os dados sobre o barramento, e consequentemente reduz o número de leituras/gravações para acessar a mesma linha de dados de cache.

A DDR5 adiciona um novo comando chamado SAME-BANK Refresh, que permite uma atualização de apenas um banco por grupo de banco, versus todos os bancos. Quando comparado com a DDR4, este comando permite que a DDR5 melhore ainda mais o desempenho e a eficiência.

A DDR5 utiliza a Equalização de Feedback de Decisão (DFE) para proporcionar uma integridade de sinal confiável e estável no módulo, exigido para grandes larguras de banda.

Enquanto os módulos de memória parecem similares ao DDR4, há mudanças significativas que fazem com que eles sejam incompatíveis com sistemas antigos. O local da chave (fenda no centro) se move para evitar que sejam instalados em soquetes incompatíveis.

Testada e aprovada, assim você pode montar o seu PC ou atualizar com confiança sua placa-mãe preferida.

| Taxas de dados (Velocidade em MT/s){{Footnote.A65242}} | 3600, 4000, 4400, 4800, 5200, 5600, 6000, 6400, 6800, 7200, 7600, 8000, 8400, 8800 |

| Densidades de DRAM monolíticas (Gbit) | 8Gb, 16Gb, 24Gb, 32Gb, 48Gb, 64Gb |

| Ballout e Tipo de Pacote (x4, x8 / x16) | BGA, 3DS TSV (78, 82 / 102) |

| Interface | |

|---|---|

| Tensão (VDD / VDDQ / VPP) | 1.1/ 1.1/ 1.8 V |

| VREF interno | VREFDQ, VREFCA, VREFCS |

| Comando/Endereço | POD (Pseudo Open Drain) |

| Equalização | DFE (Equalização de Feedback Dinâmica) |

| Comprimento de burst | BL16 / BC8 / BL32 (opcional) |

| Arquitetura principal | |

| Número de bancos | 32 bancos (8 grupos de banco) 8 BG x 4 bancos (16-64Gb x4/x8) 8 BG x 2 bancos (8Gb x4/x8) 16 bancos (4 grupos de banco) 4 BG x 4 bancos (16-64Gb x16) 4 BG x 2 bancos (8Gb x16) |

| Tamanho da página (x4 / x8 / x16) | 1KB / 1KB / 2KB |

| Pré-busca | 16n |

| DCA (Ajuste de Ciclo de Serviço) | DQS e DQ |

| Monitoramento de Atraso de DQS Interno | Oscilador de intervalo de DQS |

| ODECC (On-die ECC) | Scrub e verificação de erro 128b+8b SEC |

| CRC (Verificação de Redundância Cíclica) | Leitura/gravação |

| ODT (On-die Termination) | barramento CA, DQ, DQS, DM |

| MIR (pin “Espelho”) | Sim |

| Inversão de barramento | Inversão de Endereço/Comando (CAI) |

| Treinamento de CA, Treinamento de CS | Treinamento de CA, Treinamento de CS |

| Modos de treinamento de nivelamento de gravação | Aperfeiçoado |

| Padrões de Treinamento de Leitura | MRs dedicados para padrões de treinamento gerados por LFSR , clock e serial definido por usuário |

| Registros do modo | Até 256 x 8 bits |

| Comandos de PRÉ-CARGA | Todos os bancos, por banco e mesmo banco |

| Comandos de REFRESH | Todos os bancos e mesmo banco |

| Modo loopback | Sim |