세계 최고의 메인보드 제조업체로부터 인증 획득{{Footnote.N64682}}

테스트를 거쳐 승인을 획득한 제품이므로 사용자는 확신을 가지고 선호하는 메인보드를 사용해 조립 및 업그레이드할 수 있습니다.

DDR5는 DDR5 SDRAM으로 알려진 DDR(Double Data Rate) SDRAM 메모리의 5세대 제품입니다. 2017년에 산업 표준 조직인 JEDEC (합동 전자 장치 엔지니어링 협의회, Joint Electron Device Engineering Council)가 Kingston을 포함한 최고의 글로벌 메모리 반도체 및 칩셋 아키텍처 판매업체의 지원을 받아 시작된 DDR은 앞으로 10년 간 컴퓨터 사용에 있어서 더 높은 성능, 더 낮은 전력 그리고 더 견고한 데이터 무결성을 위한 새로운 기능을 탑재하여 제작되었습니다. DDR5는 2021년에 출시됨.

DDR5는 4800MT/s{{Footnote.A65242}}부터 시작하고, DDR4는 최대 3200MT/s입니다. 이는 대역폭이 50% 증가한 것입니다. 컴퓨팅 플랫폼 출시에 맞춰 DDR5는 표준 속도를 8800MT/s, 또는 그 이상으로 확장할 계획입니다.

1.1V에서 DDR5는 1.2V에서 DDR4의 동등한 구성요소에 비해 20% 더 적은 전력을 소비합니다. 노트북에서 배터리 수명을 연장시킴으로써 DDR5는 24시간 가동하는 기업용 서버의 경우에도 중요한 이점을 제공합니다.

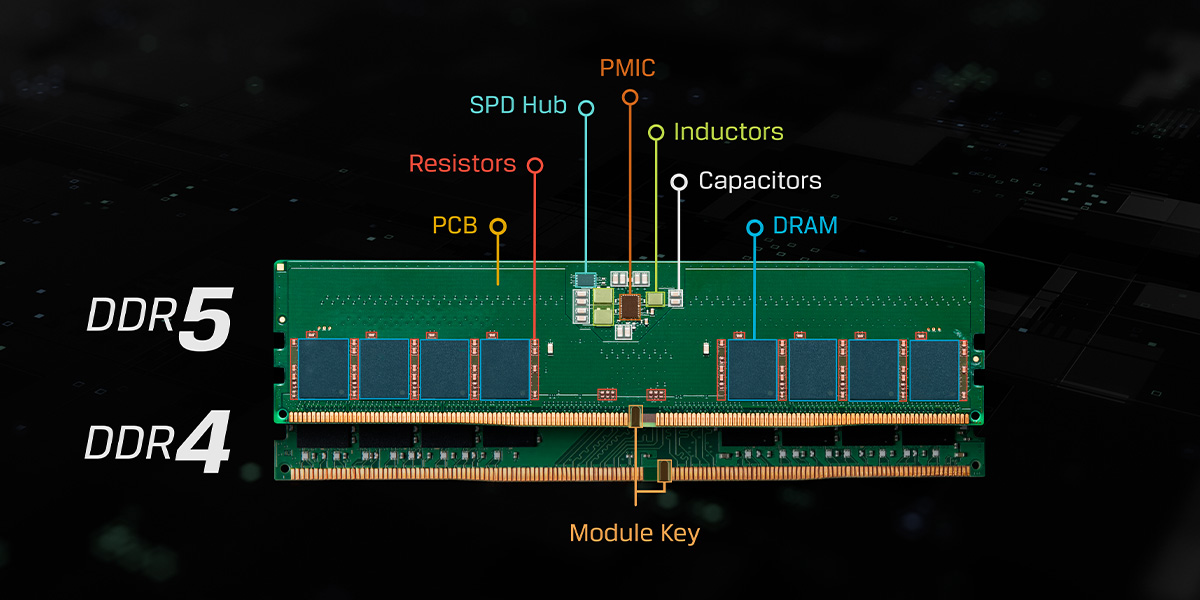

DDR5 모듈은 내장형 PMIC(전력 관리 통합 회로, Power Management Integrate Circuits)를 탑재하고 있으며 PMIC는 메모리 모듈의 다양한 구성요소(DRAM, 레지스터, SPD 허브 등)에 필요한 전력을 조절합니다. 서버 등급 모듈의 경우 PMIC는 12V를 사용하며 PC 등급 모듈의 경우 PMIC는 5V를 사용합니다. 이를 통해 이전 세대보다 더 우수한 전력 분배가 가능해지고 신호 무결성을 향상시키며 소음을 줄입니다.

DDR5는 SPD(직렬 프레즌스 검출, Serial Presence Detect) EEPROM을 추가 허브 기능과 결합하고, 외부 제어장치에 접근을 관리하며 내부 버스의 메모리 로딩을 외부와 분리시키는 새로운 장치입니다.

DDR5는 메모리 모듈을 두 개의 독립적인 32비트 지정 하위 채널로 분할하여 효율성을 높이고 메모리 제어장치의 데이터 접근 지연시간을 감소시킵니다. DDR5 모듈의 데이터 폭은 여전히 64비트이지만 두 개의 32비트 지정 채널로 분할함으로써 전체적인 성능을 향상시킵니다. 서버 등급 메모리(RDIMMs)의 경우 하위 채널당 총 40비트 또는 Rank당 80비트에 대한 ECC 지원을 위해 8비트가 각 하위 채널에 추가됩니다. 이중 Rank 모듈에는 네 개의 32비트 하위 채널이 탑재됩니다.

모듈의 중심에 있는 노치는 키와 같은 역할을 하며 설치 중에 DDR4, DDR3 또는 기타 지원되지 않는 모듈 유형을 방지하기 위해 DDR5 소켓에 맞춥니다. DDR4와 다르게 DDR5 모듈 키는 다음의 모듈 유형에서 서로 다릅니다. UDIMM 및 RDIMM

온 다이 ECC(오류 수정 코드, Error Correction Code)는 DRAM 칩 내의 비트 오류를 수정하기 위해 설계된 새로운 기능입니다. DRAM 칩이 웨이퍼 석판인쇄 축소를 통해 밀도를 증가시키기 때문에 데이터 유출 가능성이 증가합니다. 온 다이 ECC(오류 수정 코드, Error Correction Code)는 칩 내의 오류를 수정하고, 신뢰도를 높이며 결함율을 줄임으로써 위험을 완화시킵니다. 이 기술은 칩 외부 또는 CPU 내에 위치한 모듈과 메모리 제어장치 사이의 버스에 발생한 오류는 수정하지 못합니다. 서버 및 워크스테이션에 대해 ECC(오류 수정 코드, Error Correction Code)를 사용할 수 있는 프로세서는 상황에 따라 단일 또는 다중 비트 오류를 수정할 수 있는 코딩을 보유합니다. 추가적인 DRAM 비트는 이러한 수정을 할 수 있도록 사용 가능해야 하며 언버퍼, 레지스터드 및 부하 절감 ECC와 같은 ECC 등급 모듈 유형에 탑재됩니다.

서버급 DDR5 RDIMM은 모듈의 끝에 온도 센서를 추가하여 DIMM의 전체 길이에 걸쳐 열 상태를 모니터링합니다. 이는 DDR4에서 고온으로 인해 성능이 저하되는 것과 달리 시스템 냉각을 더욱 정밀하게 제어할 수 있게 해줍니다.

DDR5는 뱅크를 16에서 32까지 두 배로 증가시킵니다. 이를 통해 한 번에 더 많은 페이지가 열림으로써 효율성을 증가시킵니다. DDR4의 경우에도 최소 파열 길이가 8에서 16까지 두 배로 증가합니다. 이를 통해 데이터 버스 효율성이 향상되며 버스에서 데이터를 2회 제공한 결과 동일한 캐시 데이터 라인에 접근하는 읽기/쓰기 횟수를 감소시킵니다.

DDR5는 모든 뱅크가 아닌 뱅크 그룹당 하나의 뱅크만의 리프레시를 가능하게 하는 SAME-BANK 리프레시라고 부르는 새로운 명령어를 추가합니다. DDR4와 비교했을 때 이 명령어는 DDR5의 성능 및 효율성을 더욱 향상시킬 수 있도록 해줍니다.

DDR5는 높은 대역폭에 필요한 모듈에 안정적이고 신뢰할 수 있는 신호 무결성을 제공하기 위해 DFE(결정 피드백 이퀄라이제이션, Decision Feedback Equalization)를 활용합니다.

메모리 모듈 자체가 DDR4와 유사하게 나타나는 반면 구형 시스템과 호환되지 않도록 만드는 중요한 변경사항이 발생합니다. 호환되지 않는 소켓에 설치되지 않도록 키 위치(중심에 있는 노치)를 이동시키십시오.

테스트를 거쳐 승인을 획득한 제품이므로 사용자는 확신을 가지고 선호하는 메인보드를 사용해 조립 및 업그레이드할 수 있습니다.

| 데이터 비율(MT/s 속도){{Footnote.A65242}} | 3600, 4000, 4400, 4800, 5200, 5600, 6000, 6400, 6800, 7200, 7600, 8000, 8400, 8800 |

| 단일 DRAM 밀도(Gbit) | 8Gb, 16Gb, 24Gb, 32Gb, 48Gb, 64Gb |

| 패키지 유형 및 볼아웃(x4, x8 / x16) | BGA, 3DS TSV(78, 82 / 102) |

| 인터페이스 | |

|---|---|

| 전압 (VDD / VDDQ / VPP) | 1.1 / 1.1 / 1.8 V |

| 내부 VREF | VREFDQ, VREFCA, VREFCS |

| 명령어/주소 | POD(유사 개방 배수, Pseudo Open Drain) |

| 이퀄라이제이션 | DFE(동적 피드백 이퀄라이제이션, Dynamic Feedback Equalization) |

| 파열 길이 | BL16 / BC8 / BL32(옵션) |

| 코어 아키텍처 | |

| 뱅크의 수 | 뱅크 32개(뱅크 그룹 8개) 8 BG x 뱅크 4개(16-64Gb x4/x8) 8 BG x 뱅크 2개(8Gb x4/x8) 뱅크 16개(뱅크 그룹 4개) 4 BG x 뱅크 4개(16-64Gb x16) 4 BG x 뱅크 2개(8Gb x16) |

| 페이지 크기(x4 / x8 / x16) | 1KB / 1KB / 2KB |

| 프리페치 | 16n |

| DCA(사용률 조정, Duty Cycle Adjustment) | DQS 및 DQ |

| 내부 DQS 지연 모니터링 | DQS 간격 발진기 |

| ODECC(온 다이 ECC) | 128b+8b SEC 오류 확인 및 스크럽 |

| CRC(순환 중복 검사, Cyclic Redundancy Check) | 읽기/쓰기 |

| ODT(온 다이 종료) | DQ, DQS, DM, CA 버스 |

| MIR("미러" 핀) | 예 |

| 버스 전도 | 명령어/주소 전도(CAI) |

| CA 교육, CS 교육 | CA 교육, CS 교육 |

| 쓰기 레벨링 교육 모드 | 개선 |

| 읽기 교육 패턴 | 사용자 정의 시리얼, 클락 그리고 LFSR의 전용 MRs -교육 패턴 생성 |

| 모드 레지스터 | 최대 256 x 8비트 |

| 프리차지 명령어 | 모든 뱅크, 각 뱅크 그리고 동일한 뱅크 |

| 리프레시 명령어 | 모든 뱅크 그리고 동일한 뱅크 |

| 루프백 모드 | 예 |