Homologado por los principales fabricantes de placas base del mundo{{Footnote.N64682}}

Comprobada y homologada para que pueda diseñar y actualizar con toda confianza sobre su placa base preferida.

DDR5 es la 5ta generación de la Memoria de acceso aleatorio dinámica síncrona de doble velocidad de datos, también conocida como SDRAM DDR5. El origen de DDR5 se remonta a 2017, cuando el organismo normativo del sector JEDEC (Joint Electron Device Engineering Council), con aportaciones de los principales proveedores mundiales de semiconductores y arquitecturas de conjuntos de chips de memorias (incluyendo Kingston), diseñada con nuevas funciones para un mayor rendimiento, y menor consumo y una mejor integridad de los datos de cara a la siguiente década de informática. DDR5 debutó en 2021.

DDR5 comienza a partir de 4800MT/s{{Footnote.A65242}}, mientras que DDR4 alcanza un máximo de 3200MT/s. Esto representa un aumento del 50% en el ancho de banda. En cadencia con los lanzamientos de plataformas informáticas, DDR5 tiene previstas velocidades estándar que alcanzarán 8800MT/s, posiblemente más allá.

A 1,1 V, DDR5 consume aproximadamente un 20% menos de electricidad que DDR4, con 1,2 V. Además de prolongar la duración de la carga de las baterías de los portátiles, también supone una ventaja significativa para los servidores empresariales que funcionan continuamente.

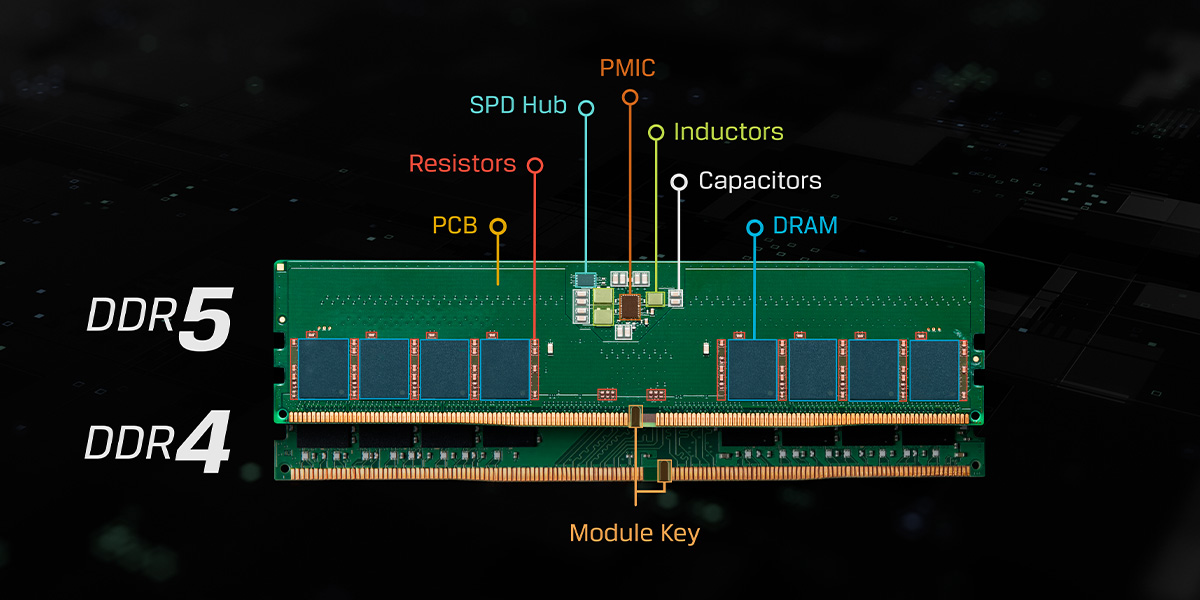

Los módulos DDR5 incorporan Circuitos integrados de gestión de energía (PMIC, por sus siglas en inglés), que ayudan a regular el consumo eléctrico de los diversos componentes del módulo de memoria (DRAM, Registro, concentrador SPD, etc.). En los módulos de grado de servidor, los PMIC utilizan 12 V, y en los de grado de PC usan 5 V. Esto optimiza la distribución de energía con respecto a las generaciones anteriores, mejorando la integridad de la señal y reduciendo el ruido.

DDR5 utiliza un nuevo dispositivo que integra la EEPROM de Detección de presencia serial (SPD, por sus siglas en inglés) con otras funciones de concentrador, administrando el acceso al controlador externo y desacoplando la carga de la memoria del bus interno del externo.

DDR5 divide el módulo de memoria en dos subcanales direccionables independientes de 32 bits para incrementar la eficiencia y reducir las latencias de accesos a los datos del controlador de memoria. La anchura de datos del módulo DDR5 sigue siendo de 64 bits, aunque dividirla en dos canales direccionables de 32 bits incrementa el rendimiento general. En las memorias de grado de servidor (RDIMM) se suman 8 bits a cada subcanal a efectos de compatibilización con ECC, con lo que se alcanza un total de 40 bits por subcanal, u 80 bits por rango. Los módulos de doble rango incorporan cuatro subcanales de 32 bits.

La muesca en el centro del módulo actúa como una llave, alineándose con los conectores DDR5 para evitar la instalación de módulos DDR4, DDR3 u otros tipos de módulos incompatibles. A diferencia de DDR4, las llaves de los módulos DDR5 son diferentes en función del tipo de módulo: UDIMM y RDIMM

El ECC (Código de corrección de errores) interno es una nueva característica diseñada para corregir errores de bits dentro del chip de la DRAM. Los chips de la DRAM incrementan su densidad retrayendo la litografía de la oblea, lo cual aumenta el potencial de pérdida de datos. ECC interno mitiga este riesgo corrigiendo los errores dentro del chip, aumentando la fiabilidad y reduciendo los índices de defectos. Esta tecnología no puede corregir los errores fuera del chip o los que se producen en el bus, entre el módulo y el controlador de memoria alojado dentro de la CPU. Los procesadores con ECC para servidores y estaciones de trabajo incorporan la codificación que puede corregir uno o múltiples errores de bits sobre la marcha. En la DRAM debe haber bits adicionales que permitan ejecutar esta corrección, que existen en tipos de módulos de grado ECC, como ECC sin búfer, registrados y de carga reducida.

Los RDIMM DDR5 de grado de servidor incorporan sensores térmicos en sus extremos para monitorizar las condiciones de temperatura en toda la longitud del DIMM. Esto permite un control más preciso de la refrigeración del sistema, frente al deficiente comportamiento de los módulos DDR4 ante altas temperaturas.

DDR5 duplica el número de bancos de 16 a 32. Esto permite abrir más páginas simultáneamente, con el consiguiente aumento de la eficiencia. También se duplica la longitud mínima de ráfaga hasta 16, desde los 8 de DDR4. Esto mejora la eficiencia del bus de datos, cargando el doble de datos en el bus y, en consecuencia, reduciendo el número de lecturas/escrituras para acceder a la misma línea de datos de caché.

DDR5 agrega un nuevo comando, llamado SAME-BANK Refresh, que permite actualizar solamente un banco de un grupo de bancos, y no todos los bancos. A diferencia de DDR4, este comando permite a DDR5 mejorar todavía más su rendimiento y eficiencia.

DDR5 utiliza la Ecualización por realimentación de decisiones (DFE, por sus siglos en inglés) para posibilitar una integridad de señal estable y fiable en el módulo, imprescindible para un alto ancho de banda.

Aunque los propios módulos de memoria parecen similares a los de DDR4, existen cambios significativos que los hacen incompatibles con los sistemas antiguos. La ubicación de la llave (muesca en el centro) se desplaza para evitar la instalación en conectores incompatibles.

Comprobada y homologada para que pueda diseñar y actualizar con toda confianza sobre su placa base preferida.

| Velocidades de datos (velocidad en MT/s){{Footnote.A65242}} | 3600, 4000, 4400, 4800, 5200, 5600, 6000, 6400, 6800, 7200, 7600, 8000, 8400, 8800 |

| Densidades de DRAM monolíticas (Gbit) | 8 Gb, 16 Gb, 24 Gb, 32 Gb, 48 Gb, 64 Gb |

| Tipo de paquete y configuración (x4, x8 / x16) | BGA, 3DS TSV (78, 82 / 102) |

| Interfaz | |

|---|---|

| Tensión (VDD / VDDQ / VPP) | 1,1 / 1,1 / 1,8 V |

| VREF interna | VREFDQ, VREFCA, VREFCS |

| Comando/Dirección | POD (Drenaje pseudo abierto) |

| Ecualización | DFE (Ecualización por realimentación de decisiones) |

| Longitud de ráfaga | BL16 / BC8 / BL32 (opcional) |

| Arquitectura de núcleo | |

| Número de bancos | 32 bancos (grupos de 8 bancos) 8 GB x 4 bancos (16-64 Gb x4/x8) 8 GB x 2 bancos (8 Gb x4/x8) 16 bancos (grupos de 4 bancos) 4 GB x 4 bancos (16-64 Gb x16) 4 GB x 2 bancos (8 Gb x16) |

| Tamaño de página (x4 / x8 / x16) | 1KB / 1KB / 2KB |

| Predireccionada | 16n |

| DCA (Ajuste del ciclo de trabajo) | DQS y DQ |

| Monitorización interna de retardo de DQS | Oscilador de intervalo de DQS |

| ODECC (ECC interno) | Comprobación y eliminación de errores de SEC de 128 b + 8 b |

| CRC (Comprobación de redundancia cíclica) | Lectura/Escritura |

| ODT (Terminación interna) | DQ, DQS, DM, bus de CA |

| MIR (patilla “espejo”) | Sí |

| Inversión de bus | Inversión de comando/dirección (CAI) |

| Enseñanza de CA, enseñanza de CS | Enseñanza de CA, enseñanza de CS |

| Modos de enseñanza de nivelado de escritura | Mejorado |

| Patrones de enseñanza de lectura | MR dedicados para serie, reloj y LFSR definidos por usuario -patrones de enseñanza generados |

| Registros de modo | Hasta 256 x 8 bits |

| Comandos de precarga | Todos los bancos, por banco y mismo banco |

| Comandos de actualización | Todos los bancos y el mismo banco |

| Modo de bucle | Sí |