Certificato dai principali produttori di schede madri globali{{Footnote.N64682}}

Testate e approvate per consentire ai clienti di assemblare e effettuare upgrade dei sistemi con la massima fiducia, utilizzando le schede madri preferite.

DDR5 è quinta generazione di memorie ad accesso casuale dinamico sincronizzato con velocità di trasferimento doppia, anche noto con il nome abbreviato SDRAM DDR5. L’origine dello standard risale al 2017, a opera dell’ente di gestione degli standard industriali JEDEC (Joint Electron Device Engineering Council), con input forniti anche dai principali produttori globali di semiconduttori e architetture chipset, tra cui Kingston. Lo standard DDR5 è progettato con nuove funzionalità per fornire maggiori prestazioni, ridotti consumi e una maggiore integrità dei dati per far fronte alle sfide informatiche del prossimo decennio. Lo standard DDR5 ha debuttato nel 2021.

La velocità minima del DDR5 è di 4800MT/s{{Footnote.A65242}}, superiore alla velocità massima dello standard DDR4 di 3200MT/s. Si tratta di un incremento del 50% in ampiezza di banda. Procedendo di pari passo con le piattaforme di elaborazione che saranno lanciate sul mercato, è stato previsto che le memorie DDR5 raggiungeranno velocità standard che cresceranno fino a raggiungere gli 8800MT/s, se non anche oltre.

Con un voltaggio pari a 1,1 V, le memorie DDR5 consumano circa il 20% in meno rispetto ai modelli DDR4 equivalenti a 1,2 V. Oltre a consentire un risparmio di batteria sui laptop, queste memorie hanno anche vantaggi notevoli sui server aziendali attivi 24 ore su 24.

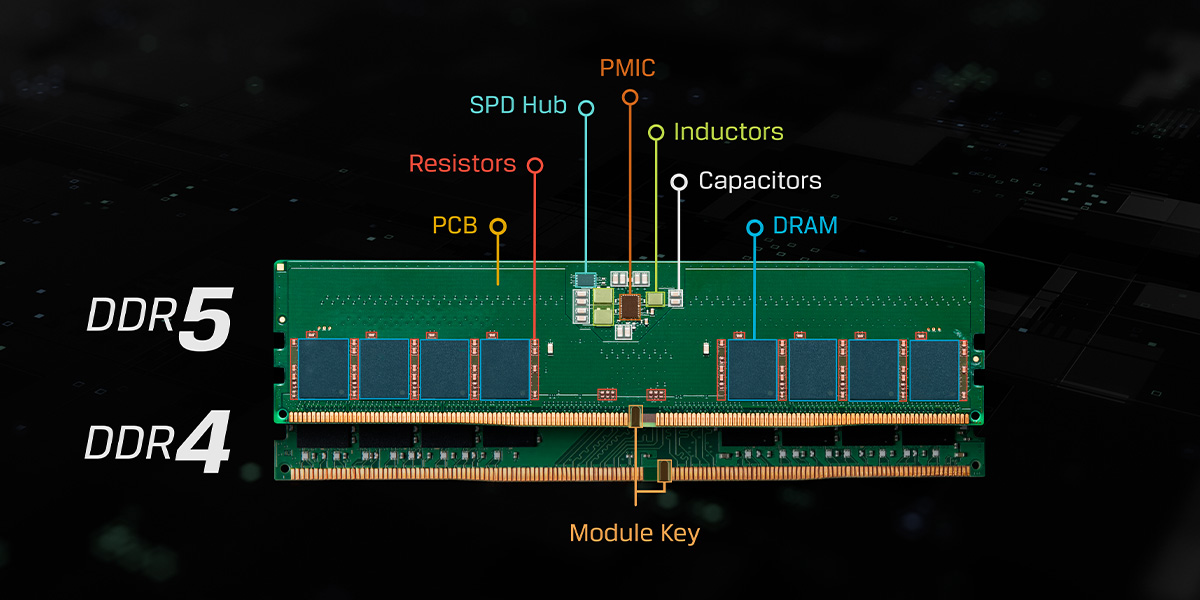

I moduli DDR5 sono equipaggiati con Circuiti integrati di gestione energetica (PMIC), che aiutano a regolare la quantità di energia richiesta dai vari componenti del modulo di memoria (DRAM, registro, hub SPD, ecc.). Nel caso dei moduli di classe server, i PMIC utilizzano 12 V, mentre i moduli per PC utilizzano PMIC da 5 V. Ciò garantisce una migliore distribuzione rispetto alle precedenti generazioni, migliorando anche l’integrità del segnale e riducendo le interferenze.

Le memorie DDR5 utilizzano un nuovo dispositivo che integra EEPROM SPD (Serial Presence Detect) con funzionalità hub aggiuntive, funzioni di gestione degli accessi al controller esterno e separazione del carico di memoria tra bus interno ed esterno.

La tecnologia DDR5 suddivide i moduli di memoria in due sottocanali indipendenti a 32-bit, al fine di accrescere l’efficienza e ridurre le latenze di accesso ai dati per il controller di memoria. La larghezza di banda dati dei moduli DDR5 è sempre a 64-bit. Tuttavia, essa è sdoppiata in due canali a 32-bit indirizzabili, con un conseguente incremento delle prestazioni complessive. Nel caso delle memorie per server (RDIMM), 8-bit vengono aggiunti a ciascun sottocanale, per il supporto ECC. Ciò equivale a un totale di 40-bit per sottocanale, o 80-bit per rank. I moduli dual rank integrano quattro sottocanali a 32-bit.

L’incavo presente sul centro del modulo funge da tacca di centraggio che consente di allineare i socket DDR5 al fine di evitare l’installazione errata di moduli DDR4 o DDR3, oppure quella di altri moduli. A differenza dei moduli DDR4, le tacche dei moduli DDR5 differiscono a seconda dei modelli: UDIMM e RDIMM

La funzione On-die ECC (Error Correction Code) è una nuova funzionalità progettata per correggere gli errori dei bit sui chip DRAM. Con il graduale incremento di densità dei chip DRAM ottenuto mediante livelli crescenti di compattezza della litografia, cresce anche il potenziale di perdita dei dati. La tecnologia On-die ECC mitiga tale rischio, correggendo gli errori sul chip e incrementando l’affidabilità e riducendo la percentuale di difetti. Questa tecnologia non consente di correggere gli errori esterni al chip, o quelli che si verificano sul bus tra il modulo e il controller della memoria alloggiato nella CPU. I processori con funzionalità ECC per server e workstation integrano funzionalità di codifica che consentono di correggere errori dei bit singoli o multipli in tempo reale. Affinché la correzione funzioni correttamente è necessario che siano disponibili bit DRAM extra sui moduli di classe ECC, come gli ECC senza buffer, registrati e con carico ridotto.

Le RDIMM DDR5 di classe server integrano anche sensori di temperatura sulle terminazioni dei moduli, al fine di monitorare le condizioni termiche sull’intera lunghezza della DIMM. Ciò consente un controllo più accurato del raffreddamento del sistema, contrariamente al throttling delle prestazioni osservato con le DDR4 in presenza di alte temperature.

Le memorie DDR5 hanno un numero doppio di banchi, che passano da 16 a 32. Ciò consente di aprire un maggior numero di pagine simultaneamente, per una maggiore efficienza. È raddoppiata anche la burst length minima, che passa da 8 nei modelli DDR4 a 16 in quelli DDR5. Ciò contribuisce a migliorare l’efficienza del bus dati, con un flusso dati raddoppiato sul bus e, di conseguenza, riducendo il numero di scritture/letture per consentire l’accesso alla stessa linea dati di cache.

Le memorie DDR5 integrano un nuovo comando chiamato SAME-BANK Refresh, che consente il refresh di un solo banco per ciascun gruppo banchi, rispetto alle tradizionali soluzioni che richiedono il refresh di tutti i banchi. Rispetto ai modelli DDR4, questo comando consente alle memorie DDR5 di migliorare ulteriormente prestazioni ed efficienza.

Le memorie DDR5 utilizzano le funzioni Decision Feedback Equalization (DFE) per garantire segnali stabili, affidabili e integri sui moduli, un requisito fondamentale con elevate larghezze di banda.

Sebbene i moduli di memoria appaiano simili ai modelli DDR4, i nuovi modelli integrano importanti modifiche che li rendono incompatibili con i sistemi legacy. La posizione della tacca (con scanalatura al centro), previene l’installazione dei moduli su socket di tipo incompatibile.

Testate e approvate per consentire ai clienti di assemblare e effettuare upgrade dei sistemi con la massima fiducia, utilizzando le schede madri preferite.

| Velocità dati (velocità in MT/s){{Footnote.A65242}} | 3600, 4000, 4400, 4800, 5200, 5600, 6000, 6400, 6800, 7200, 7600, 8000, 8400, 8800 |

| Densità DRAM monolitiche (Gbit) | 8 Gb, 16 Gb, 24 Gb, 32 Gb, 48 Gb, 64 Gb |

| Tipo pacchetto e ballout (x4, x8 / x16) | BGA, 3DS TSV (78, 82 / 102) |

| Interfaccia | |

|---|---|

| Voltaggio (VDD / VDDQ / VPP) | 1,1 / 1,1 / 1,8 V |

| VREF interno | VREFDQ, VREFCA, VREFCS |

| Comando/indirizzo | POD (Pseudo Open Drain) |

| Equalizzazione | DFE (Dynamic Feedback Equalization) |

| Burst Length | BL16 / BC8 / BL32 (opzionale) |

| Architettura core | |

| Numero di banchi | 32 banchi (8 gruppi banchi) 8 gruppi banchi x 4 banchi (16-64 Gb x4/x8) 8 gruppi banchi x 2 banchi (8 Gb x4/x8) 16 banchi (4 gruppi banchi) 4 gruppi banchi x 4 banchi (16-64 Gb x16) 4 gruppi banchi x 2 banchi (8 Gb x16) |

| Dimensione pagina (x4 / x8 / x16) | 1KB / 1KB / 2KB |

| Prefetch | 16n |

| DCA (Duty Cycle Adjustment) | DQS e DQ |

| Monitoraggio ritardo DQS interno | Oscillatore di intervallo DQS |

| ODECC (On-die ECC) | Verifica ed eliminazione errori 128b+8b SEC |

| CRC (Cyclic Redundancy Check) | Lettura / Scrittura |

| ODT (On-die Termination) | DQ, DQS, DM, CA bus |

| MIR (“Mirror” pin) | Sì |

| Inversione bus | Inversione comando/indirizzo (CAI) |

| CA Training, CS Training | CA training, CS training |

| Modalità di apprendimento per il livellamento in scrittura | Soluzione adottata |

| Pattern di apprendimento in lettura | MR dedicati per seriali definiti dall'utente, clock e pattern di apprendimento generati mediante LFSR |

| Registri di modalità | Fino a 256 x 8 bit |

| Comandi di PRECARICA | Tutti i banchi, per banco singolo e sullo stesso banco |

| Comandi REFRESH | Tutti i banchi e sullo stesso banco |

| Modalità loopback | Sì |