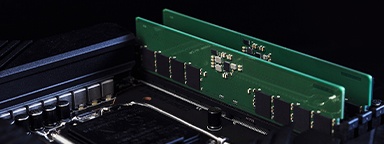

Seiring dengan makin tingginya kecepatan standar DDR5 untuk komputer desktop dan laptop generasi terbaru, stabilitas dan integritas data menjadi masalah krusial yang perlu diatasi. Peningkatan kecepatan dapat menimbulkan gangguan dan ketidakstabilan elektronik, yang dapat mengakibatkan kesalahan, hilangnya data, atau sistem yang tidak merespons. Untuk mengatasi tantangan ini, badan yang mengelola standar industri pada memori, JEDEC, menetapkan persyaratan baru pada akhir tahun 2023 untuk DIMM (Dual Inline Memory Module - Modul Memori Sebaris Ganda) DDR5 Tanpa Buffer dan SODIMM (Small Outline Dual Inline Memory Module - Modul Memori Sebaris Ganda Bentuk Kecil) DDR5. Diawali dengan penggunaan DDR5 6400MT/dtk, komponen Client Clock Driver (CKD) harus ditambahkan pada modul memori untuk menguatkan kembali sinyal clock, meminimalkan gangguan dan ketidakstabilan, serta memperbaiki integritas sinyal secara menyeluruh.

Sinyal clock, yang biasanya dihasilkan oleh prosesor, adalah sinyal tegangan dan arus yang mengalir pada frekuensi konstan serta berosilasi antara keadaan tinggi dan rendah. Dengan sinyal ini, berbagai komponen dapat melakukan sinkronisasi di seluruh motherboard sehingga data dapat dikirim dan tiba tepat waktu. Dengan terdapat pada modul, clock driver akan menghasilkan sinyal clock-nya sendiri untuk memastikan ketepatan sinkronisasi waktu pada modul.