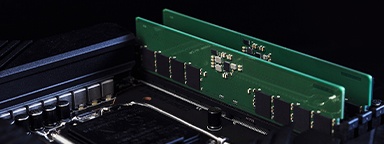

L'aumento costante di velocità dello standard DDR5 in risposta alle esigenze delle nuove generazioni di computer desktop e laptop genera problemi di stabilità e integrità dei dati che vanno assolutamente mitigati. L'aumento della velocità infatti determina la problematica del cd. rumore elettronico o jitter, potenzialmente causa di errori, perdita di dati o blocco del sistema. In risposta a questa problematica, alla fine del 2023 il JEDEC, l'organismo che definisce gli standard di settore delle memorie, ha previsto un nuovo requisito per i moduli DIMM (Dual Inline Memory Module) DDR5 senza buffer e i moduli SODIMM (Small Outline Dual Inline Memory Module) DDR5. A partire dall'introduzione delle DDR5 a 6400MT/s, i moduli di memoria devono essere dotati di un componente CKD (Client Clock Driver) che ridistribuisca il segnale di clock, riducendo al minimo il rumore e il jitter e migliori complessivamente l'integrità del segnale.

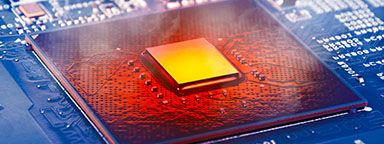

I segnali di clock, generati dal processore, sono segnali di tensione e corrente che scorrono a frequenza costante, oscillando tra stati alti e bassi. Grazie a questi segnali i componenti possono sincronizzarsi con la scheda madre, in modo che i dati vengano inviati e arrivino a tempo. Il nuovo driver del clock introdotto sul modulo genererà un proprio segnale di clock, così da garantire l'esatta sincronizzazione della temporizzazione rispetto al modulo.