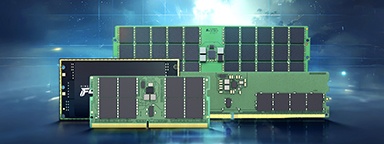

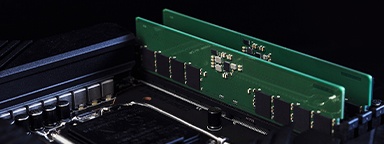

Les vitesses de la norme DDR5 devenant de plus en plus rapides pour les ordinateurs de bureau et portables de la prochaine génération, la stabilité et l’intégrité des données deviennent des problèmes critiques qu’il faut résoudre. L’augmentation de la vitesse entraîne des problèmes de bruit électronique et de gigue, ce qui peut provoquer des erreurs, des pertes de données ou des blocages du système. Pour relever ce défi, l’organisme chargé du maintien des normes industrielles en matière de mémoire, le JEDEC, a défini une nouvelle exigence fin 2023 pour les modules DDR5 DIMM Unbuffered et les modules DDR5 SODIMM. Depuis l’introduction de la DDR5 à 6 400 MT/s, un composant CKD (Client Clock Driver, pilote d’horloge client) doit être ajouté au module de mémoire pour rediriger le signal d’horloge, minimiser le bruit, la gigue et améliorer globalement l’intégrité du signal.

Les signaux d’horloge, traditionnellement générés par le processeur, sont des signaux de tension et de courant qui circulent à une fréquence constante, oscillant entre les états haut et bas. Ces signaux permettent aux composants de se synchroniser sur la carte mère, afin que les données soient envoyées et arrivent à temps. Lorsque le pilote d’horloge est installé sur le module, il génère son propre signal d’horloge afin d’assurer une synchronisation précise sur le module.