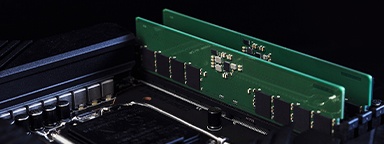

次世代デスクトップおよびノートパソコン向けに DDR5 規格の速度がますます高速化するにつれ、安定性とデータの整合性が重要な問題になっています。速度が速くなるということは、電子ノイズやジッターが問題になり、エラーやデータの損失、システムのフリーズを引き起こす可能性があるということです。この課題に対処するため、メモリの業界標準を維持する団体である JEDEC は、2023 年後半に DDR5 アンバッファード DIMM (デュアルインラインメモリモジュール) と DDR5 SODIMM (スモールアウトラインデュアルインラインメモリモジュール) に対する新しい要件を指定しました。6400MT/秒 DDR5 の導入以降、クロック信号を再駆動し、ノイズやジッターを最小限に抑え、全体的なシグナルインテグリティを向上させるために、クライアントクロックドライバー (CKD) コンポーネントをメモリモジュールに追加する必要があります。

クロック信号は、従来プロセッサが生成してきたもので、一定の周波数で流れる電圧と電流の信号であり、ハイとローの間で振動します。これらの信号により、コンポーネントがマザーボード上で同期するため、データが時間通りに送信され、到着します。モジュール上のクロックドライバーを通じて、モジュール上の正確なタイミング同期を保証するために、自身でクロック信号を生成します。