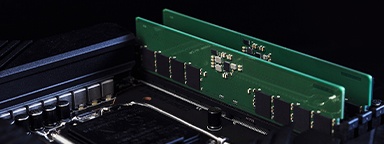

À medida que as velocidades padrão da DDR5 se tornam cada vez mais rápidas para desktop e laptop de última geração, a estabilidade e a integridade dos dados se tornam problemas críticos para mitigar. Aumentar as velocidades significa mais ruído eletrônico e a instabilidade, tornam-se crítico e resultando potencialmente em erros, perda de dados ou até congelamento do sistema. Para enfrentar este desafio, a agência que mantém os padrões industriais da memória, JEDEC, especificou uma nova exigência no final de 2023 para UDIMMs DDR5 (Unbuffered Dual Inline Memory Module) e SODIMMs DDR5 (Small Outline Dual Inline Memory Module). Começando com a introdução da DDR5 de 6400MT/s, um componente do CKD (Client Clock Driver) tem que ser adicionado ao módulo de memória para reorientar o sinal do clock, minimizando o ruído e instabilidade, ao melhorar a integridade do sinal.

Os sinais do clock, tradicionalmente gerados pelo processador, são sinais de tensão e corrente que fluem a uma frequência constante, oscilando entre seus estados alto e baixo. Estes sinais permitem que os componentes se sincronizem através da placa-mãe, para que os dados sejam enviados e cheguem ao mesmo tempo. Com o driver do clock no módulo, ele irá gerar o seu próprio sinal de clock para garantir a sincronização precisa no módulo.