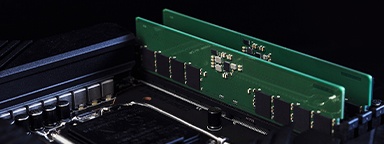

As DDR5 standard speeds get faster and faster for next-generation desktop and laptop computers, stability and data integrity become critical issues to mitigate. Increasing speeds means electronic noise and jitter become problematic, potentially resulting in errors, lost data or system freezes. To address this challenge, the body for maintaining industry standards in memory, JEDEC, specified a new requirement in late 2023 for DDR5 Unbuffered DIMMs (Dual Inline Memory Module) and DDR5 SODIMMs (Small Outline Dual Inline Memory Module). Beginning with the introduction of 6400MT/s DDR5, a Client Clock Driver (CKD) component must be added to the memory module to redrive the clock signal, which minimises noise and jitter and improves overall signal integrity.

Clock signals, traditionally generated by the processor, are voltage and current signals that flow at a constant frequency, oscillating between high and low states. These signals allow components to synchronise across the motherboard, so data is sent and arrives on time. With the clock driver on the module, it will generate its own clock signal to ensure precise timing synchronisation on the module.